FPGA Altera CycloneII EP2C5T44

From Eric

Contents |

L'installation

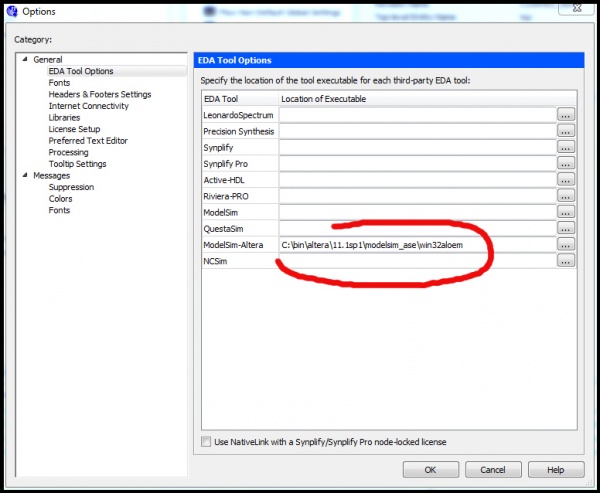

J'utilise l'environnement Quartus II Web Edition V11.1 service pack 1 et ModelSim-Altera Starter Edition.

Le transfert du bitmap vers le FPGA se fait en utilisant un clone chinois de l'USB Byte Blaster. Les drivers sont situés dans le répertoire <Path to Quartus II installation>\drivers\<cable type>.

La seule configuration consiste à indiquer quel outil de simulation on souhaite utiliser. Pour ce faire, utiliser le menu <tools>/<options> et renseigner la ligne intitulée "ModelSim-Altera" :

Un bref tutoriel

Le système cible

Le système consiste en un compteur 32 bits alimenté par une horloge à 100MHz obtenue par multiplication par 2 de l'horloge de la carte EP2C5. L'état des bits 24, 25 et 26 du compteur sera visualisé par les 3 leds de la carte à EP2C5.

La PLL est un macro-composant généré par le Macrowizard de Quartus II. Le compteur est un modèle VHDL.

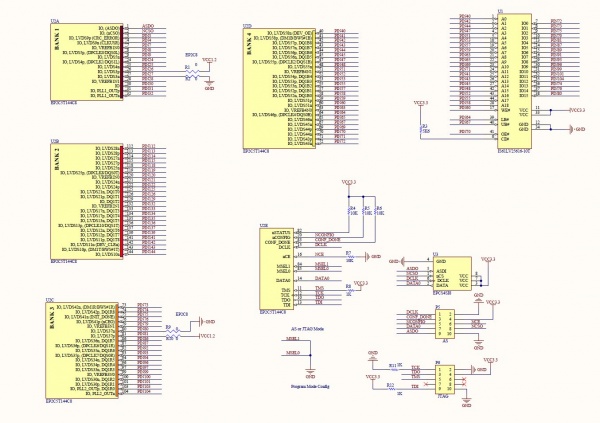

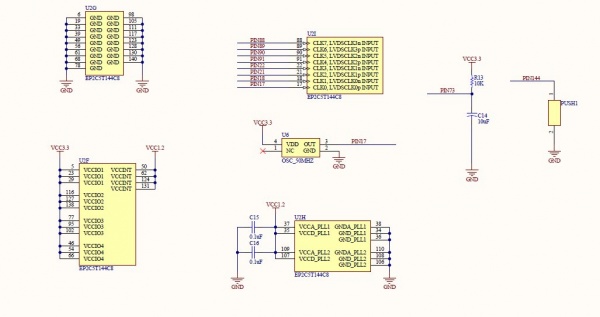

La carte

La carte que nous utilisons comprend un FPGA Cylcone II EP2C5T144 d'Altera. En voici une photo :

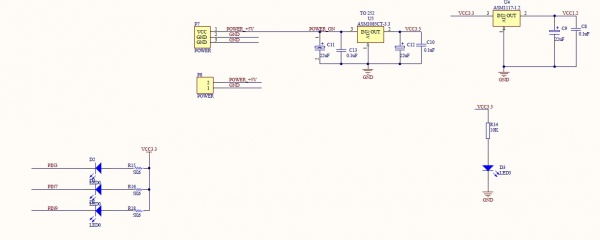

Cette carte comprend le strict minimum, à savoir :

- le FPGA lui-même,

- les connecteurs JTAG (chargement de la RAM du FPGA) et Active Serial (chargement de la flash de configuration)

- une flash de configuration de 4Mbits (EPCS4SI8)

- un régulateur 1.2V (tension du coeur)

- un régulateur 3.3V (I/O)

- 3 leds rouges connectées aux broches 3, 7 et 9

- une led rouge témoin d'alimentation

- un interrupteur connecté à la masse et à la broche 144

- un oscillateur 50MHz connecté à la broche 17.

La création du projet

Lancement du "wizard" : File/New Project Wizard

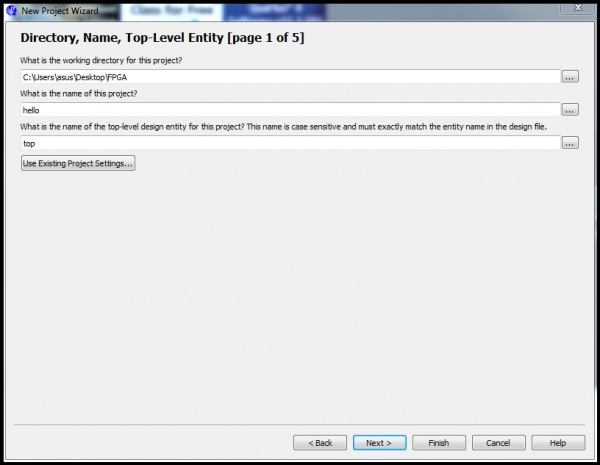

- Page 1 : on donne le nom du projet ("hello") et nom de l'entité de plus haut niveau ("top") :

- Page 2 : on laisse la page vide. Les fichiers seront rajoutés plus tard.

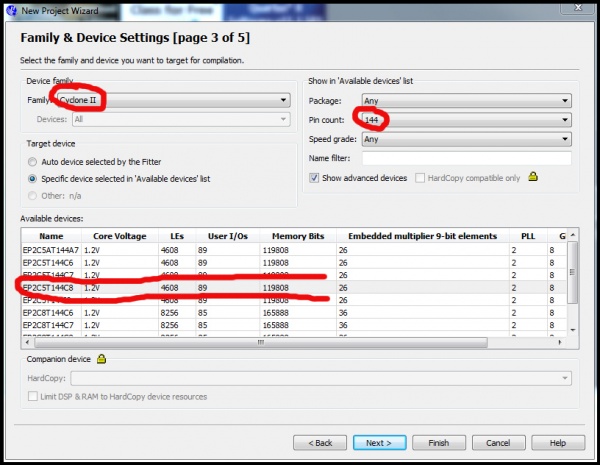

- Page 3 : sélection du composant. Il s'agit d'un CycloneII de 144 broches : l'EP2C5T144C8

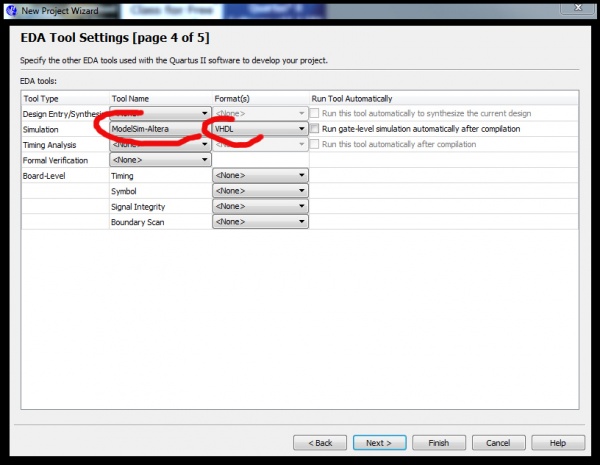

- Page 4 : sélection des outils. On précise simplement que l'on utilisera le simulateur ModelSim-Altera.

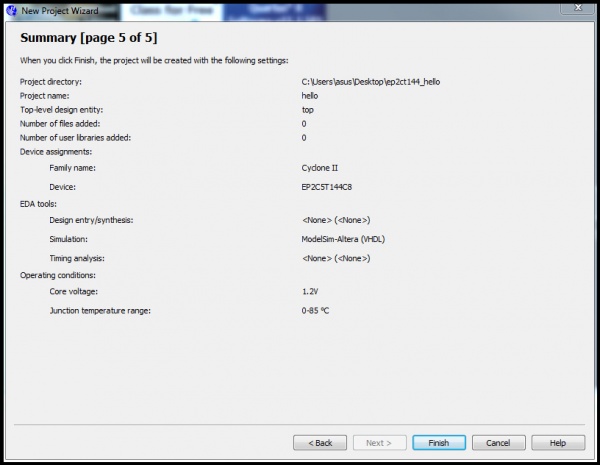

- Page 5 : résumé de la configuration du projet.

Une fois le projet créé, la page principale de QuartusII s'ouvre. Le navigateur de projet (vue "hierarchy") indique le nom du composant et le nom de l'entité de plus haut niveau (ici : "top"). Les vues "files" et "Design Units" sont pour l'instant vides.

Création du modèle VHDL

Création du compteur

Nous allons tout d'abord créer le compteur. Le code VHDL est le suivant :

library IEEE; use IEEE.STD_LOGIC_1164.all;

entity counter is port (count : buffer STD_LOGIC_VECTOR(31 downto 0) :="00000000000000000000000000000000"; clk : in STD_LOGIC; reset : in STD_LOGIC); end; architecture arch1 of counter is -- Les données de timing ne sont utilisées que pour la simulation. constant tpd_reset_to_count : time := 10 ns; constant tpd_clk_to_count : time := 5 ns; function increment(val : STD_LOGIC_VECTOR) return STD_LOGIC_VECTOR is -- normalize the indexing alias input : STD_LOGIC_VECTOR(val'length downto 1) is val; variable result : STD_LOGIC_VECTOR(input'range) := input; variable carry : STD_LOGIC := '1'; begin for i in input'low to input'high loop result(i) := input(i) xor carry; carry := input(i) and carry; exit when carry = '0'; end loop; return result; end increment; begin ctr: process(clk) begin if (clk = '1') then count <= increment(count) after tpd_clk_to_count; end if; --if (reset = '1') then -- count <= (others => '0') after tpd_reset_to_count; --end if; end process; end arch1;