Générateur BF à PLL, à base de PIC 16F628A

From Eric

Contents[hide] |

Objectifs

Utiliser une boucle à verrouillage de phase (PLL) comme multiplicateur de fréquence.

Principe

Le générateur de signal fait simplement appel à un multiplicateur de fréquence à PLL, de même nature que ce que l'on trouve dans tout bon micro-processeur ou micro-contrôleur performant. Il est en effet impossible de générer une horloge à 1GHz ou plus par la vibration mécanique d'un quartz!).

La multiplication d'une fréquence à l'aide d'un PLL consiste à

- élaborer un signal Si de fréquence précise (en utilisant un oscillateur à quartz, par exemple)

- générer un signal So à l'aide d'un VCO et diviser la fréquence de ce signal à l'aide d'un compteur

- asservir la fréquence du VCO sur la différence de phase entre Si et So.

Ainsi, freq(So) = k freq (Si)

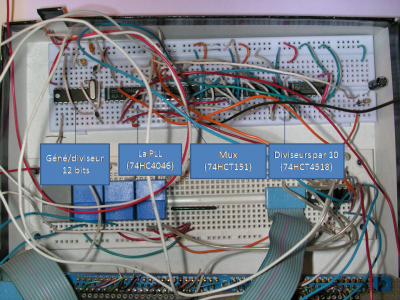

Le montage qui est présenté ci-après utilise un micro-contrôleur pour fixer le coefficient de division (IHM et compteur), et quelques composants pour réaliser : la génération du signal référence, la PLL, et la division du signal de sortie permettant de disposer d'une large gamme de fréquences de sortie.

Réalisation

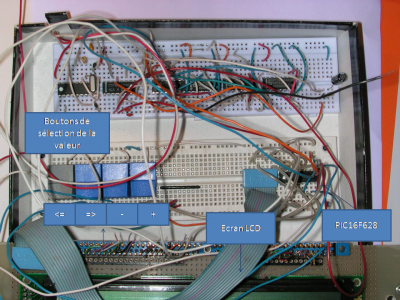

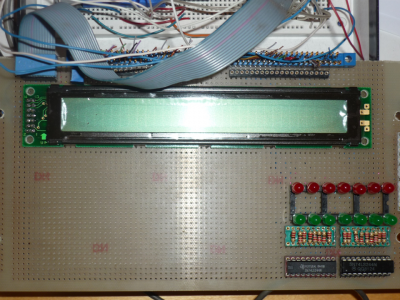

Les photos suivantes donnent un aperçu du résultat : un embrouillamini de fils... Mais ça fonctionne (enfin, presque).

La sélection de la fréquence se fait au moyen de quatre boutons qui permettent de déplacer un curseur sur le digit à modifier et à incrémenter / décrémenter la valeur du digit.